什么是芯片验证?流程是什么?

本文最后更新于 2025-03-03,文章内容可能已经过时。

一、什么是芯片验证

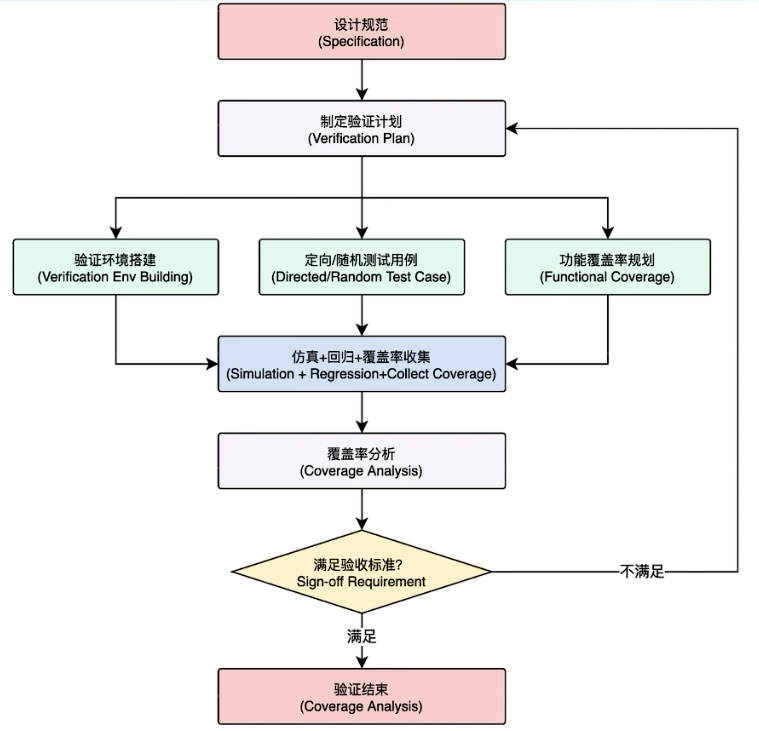

- 芯片验证从Spec定义开始

- 验证计划的重点是Feature和验证架构,然后列出Testcase

- 根据DUT搭建验证环境

- 验证计划根据验证的开展进行增补

- 直到coverage达到验收标准

- 验证要解决的问题是保证DUT功能的完备性和正确性

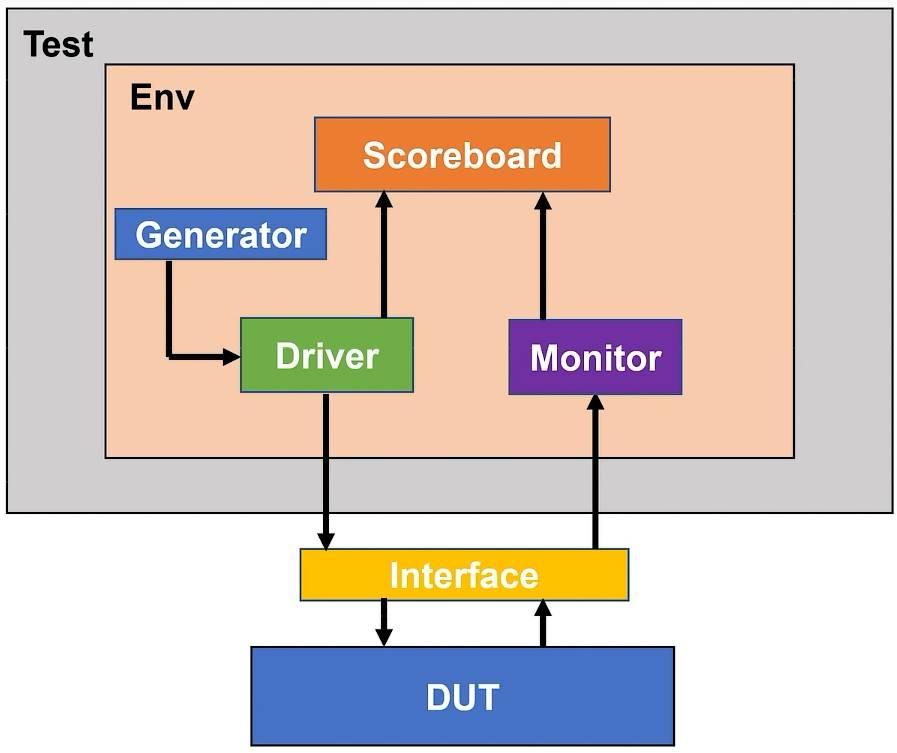

模块验证案例

设计写RTL代码称之为DUT(Design under test)待测设计

1、生成各种各样的输入激励;

2、将输入激励传到到DUT上;

3、DUT响应输入激励并输出;

4、检查输出与预期结果差异;

5、发现功能错误后修改DUT;

6、重复上述步骤收集覆盖率。

二、芯片验证的分类

1、根据芯片分类

- CPU验证

- GPU验证

- SoC验证

- MCU验证

- 等等...

2、根据工具分类

EDA验证:即功能验证,根据开发的不同阶段分为前仿验证和后仿验证。主要工具有VCS、Verdi、

NC-Verilog、ModelSim等等。

FPGA原型验证:编译设计代码,并且综合为真实的硬件电路对应FPGA板子上去,通过真实的硬件电路进行仿真(FPGA原型)。

Emulator验证:Cadence的Palladium、Mentor Graphicsl的Veloce,以及Synopsys的ZeBu等平台。

3、根据可见度分类

- 黑盒验证:验证的输入只有输入信号,输出信号和相应的功能。不需要关心内部信号和架构,验证代码对DUT内部的更改不太敏感。常用于大规模的系统级验证。

- 白盒验证:验证的输入有输入信号,输出信号,内部信号,所有的信号时序和相应功能。需要了解实际的实现方式,能够阅读RTL设计代码。常用于模块级别验证。

- 灰盒验证:黑盒验证和白盒验证的结合体,这使得验证环境得开发更加灵活。常用于子系统级别验证。

4、根据层次分类

模块验证:侧重点在模块本身功能的验证,验证计划的重点是feature和验证架构,然后列出testcase

模块能够覆盖的绝不到下一级验证去覆盖。主要内容有:检查参数设置、寄存器读写、协议检查、中断和复位、状态机跳转、工作模式覆盖、RAM的读写功能边界等等。

子系统验证:侧重点在系统的互联性,更加关注系统的工作模式和复杂场景应用。主要内容有:中断的产生、DMA功能、IP的模式功能、Memory读写等等。

系统验证:侧重点在软硬件协同仿真,关键系统路径的覆盖,芯片工作模式和测试模式以及数据通路和性能等。主要内容有:基本IP功能、CLK/RESET、IO MUX、多个P同时工作、程序的启动、工作

模式和应用场景测试。

三、芯片验证做什么

1、验证的语言

1)Verilog:在最初的时候是没有专门的验证的,验证与设计合二为一。Verilog中还包含了一个用于验证的子集,最典型的语句就是initial、task和function,纯正的设计几乎是用不到这些语言的。Verilog在验证方面最大的问题在于功能模块化、随机验证上的不足。导致更多的是direct test,而不是random test。

2)SystemC:对于算法要求非常高的设计在使用Verilog编写代码之前,会使用C或者C++建立一个算法模型即reference model,用于与DUT的输出做对比。SystemC本质上是一个C++的库,但有内存泄漏的问题,并且在构建异常的测试用例时显得力不从心。

3)SystemVerilog:它是一个Verilog的扩展集,可以完全兼容Verilog。它具有面向对象语言的特性:封装、继承和多态,同时还具有随机化、约束和功能覆盖率等特性。它提供了DPI接口,可以把C/C++的函数导入到SystemVerilog代码中。与C++相比,SystemVerilog提供内存管理机制,用户不用担心内存泄露的问题。除此之外,它还支持**系统函数 system**,用户可以把使用C++写成的参考模型编译成可执行文件,使用 system函数调用。无论是对算法类或非算法类的设计,SystemVerilog都能轻松应对。

SystemVerilog是一门优秀的语言,但依然有很多问题需要考虑,比如:

- 验证平台有哪些基本的组件,每个组件的行为有哪些?

- 验证中要建立很多测试用例,如何建立、组织的?

- 验证平台中的数据流和控制流如何分离?

- 验证平台如何保证是可重用的?

2、UVM的发展

VMM(Verification Methodology Manual),Synopsys在2006年推出的,在初期是闭源的。当OVM出现

后,面对OVM的激烈竞争,VMM开源了。VMM中集成了寄存器解决方案RAL(Register Abstraction Layer)

OVM(Open Verification Methodology),Candence和Mentor在2008年推出的,从一开始就是开源的。它引进了factory机制,功能非常强大,但是它里面没有寄存器解决方案,这是它最大的短板。针对这一情况,Candence推出了RGM,补上了这一短板。只是很遗憾的是,RGM并没有成为OVM的一部分,要想使用RGM,需要额外下载。现在OVM已经停止更新,完全被UVM代替。

UVM(Universal Verification Methodology),其前身是OVM,2010年,Accellera(SystemVerilog语言标

准最初的制定者)把OVM采纳为标准,并在此基础上着手推出新一代验证方法学UVM。由其正式版是在2011年2月由Accellera推出的,得到了Synopsys、Mentor和Cadence的支持。2011年2月,备受瞩目的UVM1.0正式版本发布。

3、验证流程

1.芯片规格

根据市场产品需求,规定芯片需要达到的功能和性能

产品和架构师根据客户提出的规格spec,商定出具体设计解决方案和实现的架构,划分出各个模块的文档;

2.测试点分解

根据spec文档,分解出具体的测试点可以分为场景类、功能类、性能类等等分解的颗粒度尽量细致,知道完备无漏一个测试点被一个case覆盖的原则分解

3.验证方案

整个芯片的验证方案一般由验证负责人规划,将设计分成多个子系统,再将子系统分成多个模块:

- 具体验证策略

- EDA工具和IT资源

- 项目进度安排

- 未覆盖的功能,风险评估

4.验证计划

定制验证策略,评估验证计划,细化testbench搭建、debug、case开发等时间,大概分为:

- spec阅读和测试点分解时间

- 开发环境和调试冒烟测试时间

- 开发case,完成全部case时间

- 回归测试和验证报告的时间

5.搭建验证平台

- 一般由激励生成器、驱动器、采样器、参考模型和计分板组成

- 从简单的功能开始,测试可以通过验证环境之后,再扩展其他功能

- 经常遇到编译报错、语法错误、预期错误,需要逐一解决

- 分析报错是由验证环境引起的,还是设计代码错误造成的

6.测试用例开发

- 冒烟测试:基本的寄存器读写测试,确保数据流已通

- 直接用例:根据spec中program流程配置的典型测试

- 随机用例:用于变量随机,覆盖更多边界,注重约束条件的配置

- 增补用例:以提高覆盖测试点为目标,增补相应的测试用例

7.回归测试

- 基本功能回归:基本功能与基本场景覆盖

- 高级功能回归:高级功能和边界测试覆盖

- 覆盖率收集回归:高级功能测试完成之后,开始收集覆盖率

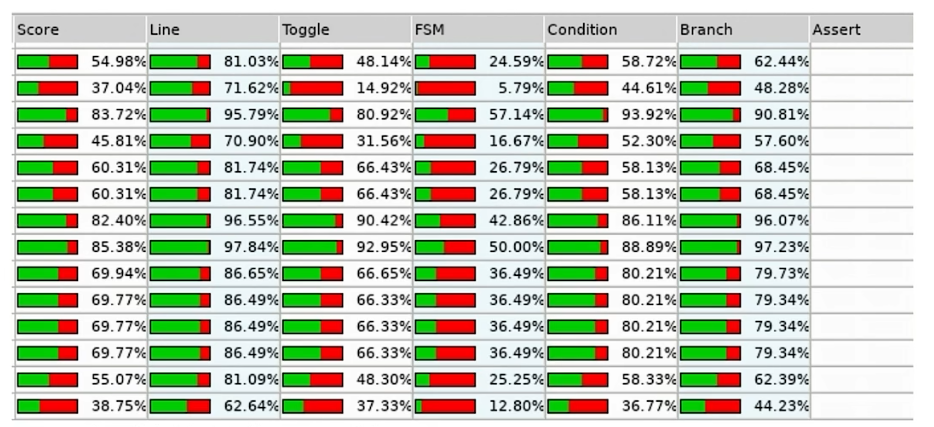

8.覆盖率分析

- 代码覆盖率

- 行覆盖率

- 条件覆盖率

- 跳转覆盖率

- 分支覆盖率

- 断言覆盖率

- 状态机覆盖率

- 功能覆盖率

9.验证报告

- 应用场景验证

- 模块复用说明

- 覆盖率分析

- 风险评估

- 待改进方案

四、验证工程师的成长

追求完美,保持创新

有大局观,注重细节

交流沟通,追根问底

要学会分享,持续的输出

向前后扩展,多学习知识

一定要有耐心和专注力,懂得团队合作

- 感谢你赐予我前进的力量